信令终端完成L2功能,由处理机、存储器和有关的控制电路组成。以下给出两个示例。

1.FETEX150系统

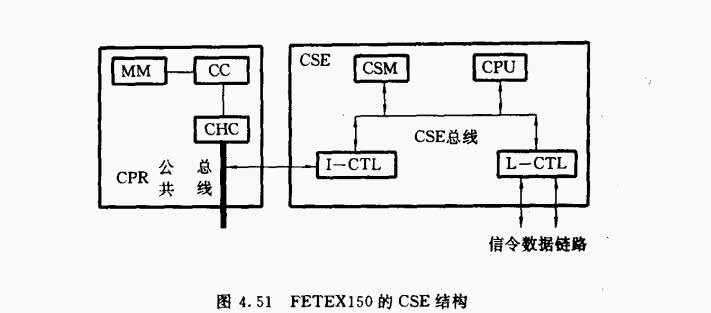

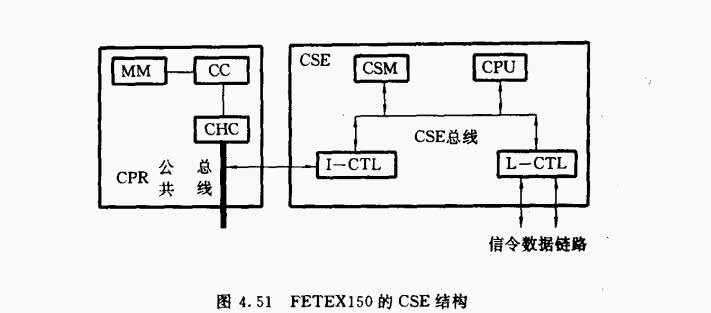

FETEX150系统中的信令终端称为CSE,其基本结构示意于图4.51。

图4.51中,链路控制器L-CTL完成L?的硬件功能,L2的软件功能固化在CPU的ROM中。CPU为8b微机,采用两个4b的位片式微机,速度可以保证信令处理的严格时间要求。链路控制器L一CTL是与公共总线的接口。CSM是共路信令存储器,用于信令收发的缓冲,有64kW,每字8b。

在CPU、CSM、L-CTL、I一CTL间由CSE总线相连。在CPU配合下,在I一CTL与CSM间及L—CTL与CSM间用DMA方式传送数据,在通道控制器CHC配合下,在I-CTL与主存储器MM间也用DMA方式传送数据。

2.S1240系统

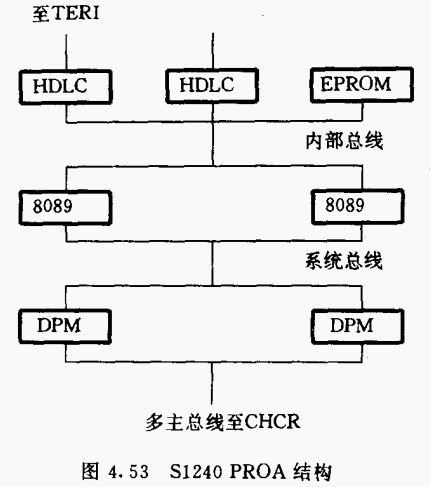

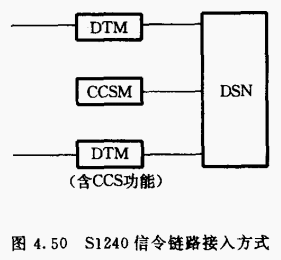

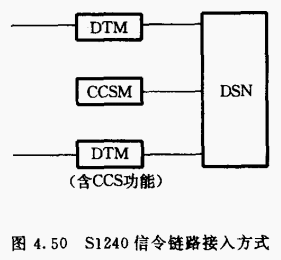

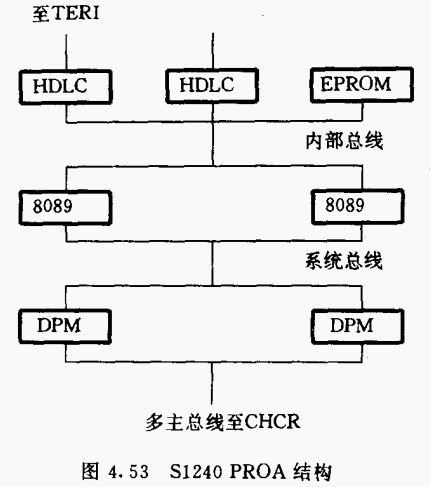

S1240系统实现L2的信号终端在CCSM中,其基本结构如图4.52所示。在CCSM的终端电路中有8块规约板PROA和一块信道控制器板CHCR。每块PROA由HDLC信号控制器,8089信令链处理机,EPROM和双端口RAM组成,如图4.53所示。每块PROA可接入两条信令链路,对应于两个HDLCO第2级软件驻存在EPROM中。双端口RAM称为局部双端口RAM,用DPM表示,是PROA与CHCR间来往信息的缓冲器。PROA与CHCR间用多主总线(multimasterbus)相连。CHCR由处理机、双端口RAM和EPROM组成,见图4.54。处理机也采用8089IOP,控制PROA和CHCR中双端口RAM之间的数据传送(DMA方式),并对PROA中的信令链处理机发送命令和收集信息。CHCR用高速总线与CCSM中的终端控制单元相连。